I. Mạch cầu H (H-Bridge Circuit).

Giả sử bạn có một động cơ DC có 2 đầu A và B, nối 2 đầu dây này với một nguồn điện DC (ắc qui điện – battery). Ai cũng biết rằng nếu nối A với cực (+), B với cực (-) mà động cơ chạy theo chiều thuận (kim đồng hồ) thì khi đảo cực đấu dây (A với (-), B với (+)) thì động cơ sẽ đảo chiều quay. Tất nhiên khi bạn là một “control guy” thì bạn không hề muốn làm công việc “động tay động chân” này (đảo chiều đấu dây), bạn ắt sẽ nghĩ đến một mạch điện có khả năng tự động thực hiện việc đảo chiều này, mạch cầu H (H-Bridge Circuit) sẽ giúp bạn. Như thế, mạch cầu H chỉ là một mạch điện giúp đảo chiều dòng điện qua một đối tượng. Tuy nhiên, rồi bạn sẽ thấy, mạch cầu H không chỉ có một tác dụng “tầm thường” như thế. Nhưng tại sao lại gọi là mạch cầu H, đơn giản là vì mạch này có hình chữ cái H. Xem minh họa trong hình 1.

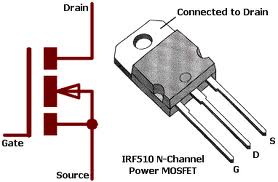

Hình 1. Mạch cầu H.

Trong hình 1, hãy xem 2 đầu V và GND là 2 đầu (+) và (-) của ắc qui, “đối tượng” là động cơ DC mà chúng ta cần điều khiển, “đối tượng” này có 2 đầu A và B, mục đích điều khiển là cho phép dòng điện qua “đối tượng” theo chiều A đến B hoặc B đến A. Thành phần chính tạo nên mạch cầu H của chúng ta chính là 4 “khóa” L1, L2, R1 và R2 (L: Left, R:Right). Ở điều kiện bình thường 4 khóa này “mở”, mạch cầu H không hoạt động. Tiếp theo chúng ta sẽ khảo sát hoạt động của mạch cầu H thông qua các hình minh họa 2a và 2b.

Hình 2. Nguyên lý hoạt động mạch cầu H.

Giả sử bằng cách nào đó (cái cách nào đó chính là nhiệm vụ của người thiết kế mạch) mà 2 khóa L1 và R2 được “đóng lại” (L2 và R1 vẫn mở), bạn dễ dàng hình dung có một dòng điện chạy từ V qua khóa L1 đến đầu A và xuyên qua đối tượng đến đầu B của nó trước khi qua khóa R2 và về GND (như hình 2a). Như thế, với giả sử này sẽ có dòng điện chạy qua đối tượng theo chiều từ A đến B. Bây giờ hãy giả sử khác đi rằng R1 và L2 đóng trong khi L1 và R2 mở, dòng điện lại xuất hiện và lần này nó sẽ chạy qua đối tượng theo chiều từ B đến A như trong hình 2b (V->R1->B->A->L2->GND). Vậy là đã rõ, chúng ta có thể dùng mạch cầu H để đảo chiều dòng điện qua một “đối tượng” (hay cụ thể, đảo chiều quay động cơ) bằng “một cách nào đó”.

Chuyện gì sẽ xảy ra nếu ai đó đóng đồng thời 2 khóa ở cùng một bên (L1 và L2 hoặc R1 và R2) hoặc thậm chí đóng cả 4 khóa? Rất dễ tìm câu trả lời, đó là hiện tượng “ngắn mạch” (short circuit), V và GND gần như nối trực tiếp với nhau và hiển nhiên ắc qui sẽ bị hỏng hoặc nguy hiểm hơn là cháy nổ mạch xảy ra. Cách đóng các khóa như thế này là điều “đại kị” đối với mạch cầu H. Để tránh việc này xảy ra, người ta thường dùng thêm các mạch logic để kích cầu H, chúng ta sẽ biết rõ hơn về mạch logic này trong các phần sau.

Giả thuyết cuối cùng là 2 trường hợp các khóa ở phần dưới hoặc phần trên cùng đóng (ví dụ L1 và R1 cùng đóng, L2 và R2 cùng mở). Với trường hợp này, cả 2 đầu A, B của “đối tượng” cùng nối với một mức điện áp và sẽ không có dòng điện nào chạy qua, mạch cầu H không hoạt động. Đây có thể coi là một cách “thắng” động cơ (nhưng không phải lúc nào cũng có tác dụng). Nói chung, chúng ta nên tránh trường hợp này xảy ra, nếu muốn mạch cầu không hoạt động thì nên mở tất cả các khóa thay vì dùng trường hợp này.

Sau khi đã cơ bản nắm được nguyên lý hoạt động của mạch cầu H, phần tiếp theo chúng ta sẽ khảo sát cách thiết kế mạch này bằng các loại linh kiện cụ thể. Như tôi đã trình bày trong phần trước, thành phần chính của mạch cầu H chính là các “khóa”, việc chọn linh kiện để làm các khóa này phụ thuộc vào mục đích sử dụng mạch cầu, loại đối tượng cần điều khiển, công suất tiêu thụ của đối tượng và cả hiểu biết, điều kiện của người thiết kế. Nhìn chung, các khóa của mạch cầu H thường được chế tạo bằng relay, BJT (Bipolar Junction Transistor) hay MOSFET (Metal Oxide Semiconductor Field-Effect Transistor). Phần thiết kế mạch cầu H vì vậy sẽ tập trung vào 3 loại linh kiện này. Trong mỗi cách thiết kế, tôi sẽ giải thích ngắn gọn nguyên lý cấu tạo và hoạt động của từng loại linh kiện để bạn đọc dễ nắm bắt hơn.

Relay là một dạng “công tắc” (switch) cơ điện (electrical mechanical device, không phải cơ điện tử đâu nhé :) ). Gọi là công tắc cơ điện vì chúng gồm các tiếp điểm cơ được điều khiển đóng mở bằng dòng điện. Với khả năng đóng mở các tiếp điểm, Relay đúng là một lựa chọn tốt để làm khóa cho mạch cầu H. Thêm nữa chúng lại được điều khiển bằng tín hiệu điện, nghĩa là chúng ta có thể dùng AVR (hay bất kỳ chip điều khiển nào) để điều khiển Relay, qua đó điều khiển mạch cầu H. Hãy quan sát cấu tạo và hình dáng của một loại Relay thông dụng trong hình 3.

Hình 3. Cấu tạo và hình dáng Relay.

Hình 3a (phía trên) mô tả cấu tạo của 1 Relay 2 tiếp điểm. Có 3 cực trên Relay này. Cực C gọi là cực chung (Common), cực NC là tiếp điểm thường đóng (Normal Closed) và NO là tiếp điểm thường mở (Normal Open). Trong điều kiện bình thường, khi Relay không hoạt động, do lực kéo của lò xo bên trái thanh nam châm sẽ tiếp xúc với tiếp điểm NC tạo thành một kết nối giữa C và NC, chính vì thế NC được gọi là tiếp điểm thường đóng (bình thường đã đóng). Khi một điện áp được áp vào 2 đường kích Solenoid (cuộn dây của nam châm điện), nam châm điện tạo ra 1 lực từ kéo thanh nam châm xuống, lúc này thanh nam châm không tiếp xúc với tiếp điểm NC nữa mà chuyển sang tiếp xúc với tiếp điểm NO tạo thành một kết nối giữa C và NO. Hoạt động này tương tự 1 công tắc chuyển được điều khiển bởi điện áp kích Solenoid. Một đặc điểm rất quan trọng trong cách hoạt động “đóng – mở” của Relay là tính “cách li”. Hai đường kích nam châm điện hoàn toàn cách li với các tiếp điểm của Relay , và vì thế sẽ rất an toàn. Có 2 thông số quan trọng cho 1 Relay là điện áp kích Solenoid và dòng lớn nhất mà các điểm điểm chịu được. Điện áp kích solenoid thường là 5V, 12V hoặc 24V, việc kích solenoid chính là công việc của chip điều khiển (ví dụ AVR). Vì tiếp xúc giữa cực C và các tiếp điểm là dạng tiếp xúc tạm thời, không cố định nên rất dễ bị hở mạch. Nếu dòng điện qua tiếp điểm quá lớn, nhiệt có thể sinh ra lớn và làm hở tiếp xúc. Vì thế chúng ta cần tính toán dòng điện tối đa trong ứng dụng của mình để chọn Relay phù hợp.

Hình 3a (phía dưới) là ký hiệu của một Relay mà bạn có thể gặp trong các phần mềm thiết kế mạch điện tử. Trong ký hiệu này, chân 1 là chân C, chân 2 là tiếp điểm NC và chân 3 là tiếp điểm NO, trong khi đó hai chân 4 và 5 là 2 đầu của cuộn solenoid. Chúng ta sẽ dùng ký hiệu này khi vẽ mạch cầu H dùng Relay . Sơ đồ một mạch cầu H đầu đủ dùng Relay được minh họa trong hình 4.

Hình 4. Mạch cầu H dùng Relay .

Trong mạch cầu H dùng Relay ở hình 4, 4 diode được dùng để chống hiện tượng dòng ngược (nhất là khi điều khiển động cơ). Các đường kích solenoid không được nối trực tiếp với chip điều khiển mà thông qua các transistor, việc kích các transistor lại được thực hiện qua các điện trở. Tạm thời chúng ta gọi tổ hợp điện trở + transistor là “mạch kích”, tôi sẽ giải thích rõ hơn hoạt động của mạch kích trong phần tiếp theo.

Mạch cầu H dùng Relay có ưu điểm là dễ chế tạo, chịu dòng cao, đặc biệt nếu thay Relay bằng các linh kiện tương đương như contactor, dòng điện tải có thể lên đến hàng trăm ampere. Tuy nhiên, do là thiết bị “cơ khí” nên tốc độ đóng/mở của Relay rất chậm, nếu đóng mở quá nhanh có thể dẫn đến hiện tượng “dính” tiếp điểm và hư hỏng. Vì vậy, mạch cầu H bằng Relay không được dùng trong phương pháp điều khiển tốc độ động cơ bằng PWM. Trong phần tiếp theo chúng ta sẽ tìm hiểu các linh điện có thể thay thế Relay trong mạch cầu H, gọi là các “khóa điện tử” với khả năng đóng/mở lên đến hàng nghìn hoặc triệu lần trên mỗi giây.

BJT là viết tắt của từ Bipolar Junction Transistor là một linh kiện bán dẫn (semiconductor device) có 3 cực tương ứng với 3 lớp bán dẫn trong cấu tạo. Trong tất cả các tài liệu về điện tử cơ bản đều giải thích về bán dẫn và BJT, trong tài liệu này tôi chỉ giới thiệu khái quát cấu tạo của transistor và chủ yếu là các chế độ hoạt động của transistor.

Bán dẫn là các nguyên tố thuộc nhóm IV trong bảng tuần hoàn hóa học, Silic (Si) là một ví dụ điển hình, các nguyên tố này có 4 electron ở lớp ngoài cùng. Ở trạng thái thường, Si là chất dẫn điện kém (gần như không dẫn điện), khi nhiệt độ tăng, các electron dao động mạnh và dễ dàng bị “bứt” ra khỏi tinh thể và do đó tính dẫn điện của bán dẫn sẽ tăng. Tuy nhiên, bán dẫn được dùng để chế tạo linh kiện điện tử không phải là các tinh thể thuần khiết mà có pha “tạp chất”. Nếu pha nguyên tố nhóm V (như Photpho) vào Si, 4 electron lớp ngoài cùng của P tạo liên kết công hóa trị với Si và có 1 electron của P bị “thừa” (vì P có 5 electron lớp ngoài cùng). Chất bán dẫn có pha Photpho vì thế rất dễ dẫn điện và có tính chất “âm” nên gọi là bán dẫn loại n (Negative), “hạt dẫn” trong bán dẫn loại n là electron (e thừa). Trường hợp nguyên tố nhóm III, như Bo (Boron), được pha vào Si, 3 electron lớp ngoài cùng của Bo kết hợp với 4 electron của Si tuy nhiên vẫn còn 1 “chỗ trống” sẵn sàng nhận electron. “Chỗ trống” này được gọi là “lỗ trống” và có tính chất như 1 loại hạt dẫn dương. Bán dẫn loại này vì thế gọi là bán dẫn loại p (Positive). Mức độ pha tạp chất quyết định độ dẫn của bán dẫn. Tuy nhiên, bán dẫn có pha tạp chất dù đã cải thiện tính dẫn điện vẫn không có nhiều tác dụng, “điều kỳ diệu” chỉ xảy ra khi ghép chúng lại với nhau.

Khi ghép bán dẫn loại p và loại n với nhau tạo thành tiếp xúc p-n (p-n junction), đây chính là các diode. Đặc điểm của tiếp xúc p-n là chỉ có dòng điện chạy qua theo 1 chiều từ p sang n. Khi ghép 3 lớp bán dẫn sẽ tạo thành transistor, phụ thuộc vào thứ tự bán dẫn được ghép chúng ta có transistor npn hay pnp. Tôi sẽ chọn transistor npn để giải thích hoạt động của transistor vì loại này được dùng phổ biến trong các ứng dụng điều khiển (và cả trong mạch cầu H). Hình 5 là mô hình và ký kiệu của transistor npn.

Hình 5. Transistor npn.

Ba lớp bán dẫn n, p và n kết hợp tạo thành 3 cực C (cực thu-Collector), cực B (nền – Base) và cực E (phát – Emitter). Tùy theo cách mắc transistor mà người ta có các loại phân cực khác nhau, trong hình 6 tôi trình bày cách phân cực rất cơ bản mà chúng ta sẽ dùng sau này, phân cực E chung (CE- Common Emitter).

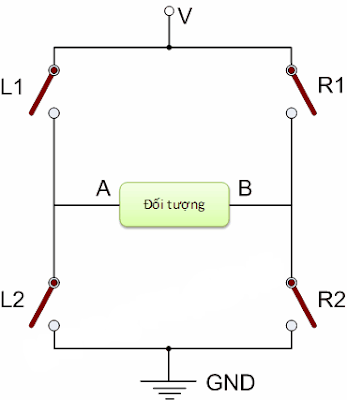

Hình 6. Phân cực E chung cho npn BJT.

Tuy là được tạo nên từ các bán dẫn tạp chất nhưng nồng độ tạp chất của các lớp trong npn BJT rất khác nhau. Lớp E rất “giàu” hạt dẫn, kế đến là lớp C và lớp B thì lại rất ít hạt dẫn và rất mỏng. Khi điện áp cực B lớn hơn điện áp cực E, tiếp xúc p-n giữa B và E được phân cực thuận. Dòng electron từ E (vốn có rất nhiều do cách pha tạp chất) ào ạt “chảy” về B, trong khi lớp B (bán dẫn loại p) vốn rất mỏng và nghèo hạt dẫn (lỗ trống), nên phần lớn electron từ E sẽ “tràn” qua cực C và đi về nguồn Vc như mô tả trên hình 6. Chú ý trên hình 6 tôi vẽ chiều di chuyển là chiều của dòng electron, chiều dòng điện sẽ ngược lại (vì theo định nghĩa chiều dòng điện ngược chiều electron). Diễn giải đơn giản, dòng diện từ cực B đã gây ra dòng điện từ cực C về E. Quan hệ của các dòng điện như sau:

IE=IB+IC (1)

Một đặc điểm thú vị là dòng electron tràn qua cực C sẽ tỉ lệ với dòng electron đến cực B. mối quan hệ như sau:

IC=hfeIB (2)

Thông số hfe gọi là hệ số khuyếch đại tĩnh (DC Current Gain) của BJT và là hằng số được ghi bởi các nhà sản xuất, nó chính là đặc tính để phân biệt từng loại BJT, gái trị của thường rất lớn, từ vài chục đến vài trăm. Chính vì đặc điểm này mà transistor được dùng như là một linh kiện “khuyếch đại”. Hãy quan sát phần mạch điện bên phải trong hình 6 (phía Vc), nếu giả sử đoạn CE của BJT là một “điện trở”, xem lại công thức (2), nếu tăng dòng điện IB thì dòng IC sẽ tăng theo trong khi điện trở RC và nguồn VC lại không đổi, rõ ràng “điện trở EC” đang giảm. Nói cách khác, dòng IB sẽ làm giảm điện trở giữa 2 cực CE của BJT. Tiếp tực tăng IB thì điều gì xảy ra, điện trở giữa 2 cực CE sẽ giảm đến giá trị nhỏ nhất có thể của nó (thường gần bằng 0, giá trị này được ghi trong datasheet mỗi loại của BJT). Khi điện trở CE đạt giá trị min, phần mạch điện bên phải gần như cố định (VC, RC, RCE) nên dòng IC cũng đạt giá trị max và gần như không thay đổi cho dù có tăng IB. Quan hệ giữa IB và IC không còn đúng như công thức (2). Hiện tượng này gọi là bão hòa, đây là hiện tượng rất quan trọng của transistor, nó là cơ sở cho sự phát triển của các mạch điện tử số (điều này giải thích tại sao người ta hay đề cập đến số lượng transistor trong các chip số, như vi xử lí cho máy tính chẳng hạn). Một cách tổng quát, điều kiện để BJT rơi vào trạng thái bão hòa là ICmax < hfeIB. Khi BJT bão hòa nó sẽ hoạt động như một “khóa điện tử”, hãy xem hình 7.

Hình 7. Khóa điện tử BJT.

Giả sử trong mạch điện ở hình 7 RB=330, RC=10K , hệ số khuyếch đại tĩnh của transistor là 100. Khi điện áp ở ngõ vào Vi=0V, BJT không hoạt động, dòng điện qua RC bằng 0 (hoặc rất nhỏ), điện áp ngõ ra Vo=12V. Khi Vi được kích kích bởi điện áp 5V, dòng IB=(5 - 0.7)/330=0.013A trong đó 0.7 là điện áp rơi trên BE. Dòng IC đạt giá trị lớn nhất khi VCE=0V, khi đó ICmax =12/10K=0.0012A. Rõ ràng IC < hfeIB và BJT sẽ bão hòa. Khi BJT bão hòa, VCE=0V và ngõ ra Vo được “nối” với GND nên Vo=0V . Tóm lại, bằng cách thay đổi mức điện áp Vi từ 0V sang 5V, điện áp ngõ ra sẽ được “switch” từ 12V sang 0V. Hoạt động của BJT khi bão hòa đôi khi còn được gọi là khuyếch đại điện áp. Vì chế độ bão hòa, BJT có thể được dùng làm các khóa điện tử trong mạch cầu H. Bạn hãy dùng chế độ bão hòa cùa BJT để tự giải thích hoạt động của 4 BJT 2N3904 dùng trong mạch cầu H ở hình 4.

Mạch điện trong hình 7 gọi là E chung. Mạch E chung của BJT hoạt động rất tốt trong chế độ khóa điện tử. Nếu chúng thay điện trở bằng động cơ thì mạch này tương đương với phần phía dưới của mạch cầu H (BJT tương đương với khóa L2 hoặc R2 trong hình 1). Câu hỏi đặt ra là có thể dùng thêm 1 BJT npn như trên để làm phần trên của mạch cầu H. Hãy xét mạch điện trong hình 8.

Hình 8. Mạch C chung.

Mạch điện trong hình 8 gọi là mạch C chung, điểm khác biệt duy nhất của mạch điện này so với hình 7 là điện trở RCđược dời xuống phía dưới cực E nên gọi là RE. Không cần khảo sát phần cực C hãy khảo sát mạch Vi -> B ->E -> RE -> GND. Khi Vi=5V, do điện áp rơi trên BE luôn là 0.7V (đặc điểm của tiếp xúc pn khi dẫn điện) nên điện áp rơi trên điện trở RE luôn là 4.3V mặc dù điện áp cực C là 12V, như thế điện áp giữa 2 cực CE là 12 - 4.3 = 7.7V. Điều này được hiểu là giữa CE có một “điện trở” khá lớn, “khóa điện tử” không hoạt động tốt đối với mạch C chung. Nếu RE là một motor DC loại 12V thì rõ ràng motor không hoạt động tốt vì điện áp rơi trên nó chỉ có 4.3V. Mặc khác điện áp CE quá lớn có thể gây hỏng BJT. Vì lí do này nếu bạn dùng BJT npn làm phần trên của mạch cầu H, BJT này sẽ rất mau hỏng (rất nóng) và mạch không hoạt động tốt. Như vậy, một chú ý khi thiết kế khóa điện tử dùng BJT là “tải” phải được đặt phía trên BJT tức là nên dùng mạch E chung như trong hình 7.

Quay lại mạch cầu H, giải pháp để vượt qua nhược điểm đề cập ở trên là sử dụng BJT loại pnp cho phần trên của mạch cầu H. Nguyên lý hoạt động của BJT pnp cũng na ná npn nhưng chiều dòng điện thì ngược lại. Với các khóa điện tử dùng BJT loại pnp, để kích khóa thì điện áp cực B được kéo xuống thấp thay vì kéo lên cao như trong hình 7. Chúng ta hãy khảo sát một một ví dụ trong hình 9.

Hình 9. Mạch E chung dùng BJT pnp.

Mũi tên trong ký hiệu của BJT pnp hướng từ E vào B, ngược lại với BJT npn. Nếu điện áp Vi=12V=VE hoặc ngõ Vi không được kết nối thì BJT không hoạt động, không có dòng điện qua RC vì dòng IB =0 nên dòng IC =0. Khi Vi=0V thì dòng IB xuất hiện và xuất hiện dòng IC (từ cực E) , nếu dòng IB đủ lớn sẽ gây bão hòa BJT và điện áp VEC gần bằng 0V hay điện áp rơi trên RC gần bằng 12V, khóa hoạt động rất tốt. Do đó, BJT pnp thường được dùng làm phần trên trong các mạch cầu H. Một điều thú vị là mạch điện trong hình 9 cũng là một mạch E chung.

Có lẽ đã đến lúc chúng ta di thiết kết một mạch cầu H hoàn chỉnh dùng BJT. Trong hình 10 tôi giới thiệu một cách thiết kế, đây không phải là cách duy nhất nhưng tôi sẽ dùng mạch này trong việc giải thích và ví dụ điều khiển (nếu có). Bạn có thể “chế” lại tùy thích miễn sao đảm bảo tất cả các BJT phải rơi vào trạng thái bão hòa khi được kích.

Hình 10. Mạch cầu H dùng BJT.

Tôi chọn 2 loại BJT công suất trung bình TIP41C và TIP42C để làm mạch cầu. Điện áp cao nhất mà 2 loai BJT này chịu được là 100V và dòng tối đa là 6A (chỉ là danh nghĩa, thực tế có thể thấp hơn). BJT npn TIP41C có thể kích trực tiếp, riêng BJT pnp TIP42C cần dùng thêm 1 BJT loại npn 2N3904 làm “mạch kích”. Khi điện áp ngõ L1 ở mức thấp, BJT Q0-1 không hoạt động, không tồn tại dòng IC của BJT này, nghĩa là không có dòng IB của BJT Q1, Q1 vì thế không hoạt động và tương đương một khóa Q1 mở. Khi L1 được kéo lên mức cao, 5V, BJT Q0-1 bão hòa (mạch E chung), dòng IC của Q0-1 xuất hiện và cũng là dòng IB của BJT Q1. Q1 vì thế cũng bão hòa và tương đương một khóa đóng. Như vậy, chúng ta có thể dùng các mức điện áp chuẩn 0V và 5V để kích các BJT dùng trong mạch cầu H cho dù điện áp nguồn có thể lên vài chục hay trăm Volt. Các đường L1, L2, R1 và R2 sẽ được vi điều khiển (AVR) điều khiển. Do BJT có thể được kích ở tốc độ rất cao nên ngoài chức năng đảo chiều, mạch cầu H dùng BJT có thể dùng điều khiển tốc độ motor bằng cách áp tín hiệu PWM vào các đường kích (thảo luận sau).

Nhược điểm lớn nhất của mạch cầu H dùng BJT là công suất của BJT thường nhỏ, vì vậy với motor công suất lớn thì BJT ít được sử dụng. Mạch điện kích cho BJT cần tính toán rất kỹ để đưa BJT vào trạng thái bão hòa, nếu không sẽ hỏng BJT. Mặt khác, điện trở CE của BJT khi bão hòa cũng tương đối lớn, BJT vì vậy có thể bị nóng…Trong phần tiếp theo tôi giới thiệu một loại linh kiện khác thường dùng làm mạch cầu H, MOSFET.

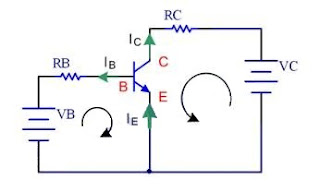

MOSFET là viết tắt của cụm Meta Oxide Semiconductor Field-Effect Transistor tức Transisor hiệu ứng trường có dùng kim loại và oxit bán dẫn. Hình 11 mô tả cấu tạo của MOSFET kênh n và ký hiệu của 2 loại MOSFET kênh n và kênh p.

Hình 11. MOSFET.

MOSFET có 3 chân gọi là Gate (G), Drain (D) và Source (S) tương ứng với B, E và C của BJT. Bạn có thể nguyên lý hoạt động của MOSFET ở các tài liệu về điện tử, ở đây chỉ mô tả các kích hoạt MOSFET. Cơ bản, đối với MOSFET kênh N, nếu điện áp chân G lớn hơn chân S khoảng từ 3V thì MOSFET bão hòa hay dẫn. Khi đó điện trở giữa 2 chân D và S rất nhỏ (gọi là điện trở dẫn DS), MOSFET tương đương với một khóa đóng. Ngược lại, với MOSFET kênh P, khi điện áp chân G nhỏ hơn điện áp chân S khoảng 3V thì MOSFET dẫn, điện trở dẫn cũng rất nhỏ. Vì tính dẫn của MOSFET phụ thuộc vào điện áp chân G (khác với BJT, tính dẫn phụ thuộc vào dòng IB), MOSFET được gọi là linh kiện điều khiển bằng điện áp, rất lý tưởng cho các mạch số nơi mà điện áp được dùng làm mức logic (ví dụ 0V là mức 0, 5V là mức 1).

MOSFET thường được dùng thay các BJT trong các mạch cầu H vì dòng mà linh kiện bán dẫn này có thể dẫn rất cao, thích hợp cho các mạch công suất lớn. Do cách thức hoạt động, có thể hình dung MOSFET kênh N tương đương một BJT loại npn và MOSFET kênh P tương đương BJT loại pnp. Thông thường các nhà sản xuất MOSFET thường tạo ra 1 cặp MOSFET gồm 1 linh kiện kênh N và 1 linh kiện kênh P, 2 MOSFET này có thông số tương đồng nhau và thường được dùng cùng nhau. Một ví dụ dùng 2 MOSFET tương đồng là các mạch số CMOS (Complemetary MOS). Cũng giống như BJT, khi dùng MOSFET cho mạch cầu H, mỗi loại MOSFET chỉ thích hợp với 1 vị trí nhất định, MOSFET kênh N được dùng cho các khóa phía dưới và MOSFET kênh P dùng cho các khóa phía trên. Để giải thích, hãy ví dụ một MOSFET kênh N được dùng điều khiển motor DC như trong hình 12.

Hình 12. Dùng MOSFET kênh N điều khiển motor DC.

Ban đầu MOSFET ko được kích, ko có dòng điện trong mạch, điện áp chân S bằng 0. Khi MOSFET được kích và dẫn, điện trở dẫn DS rất nhỏ so với trở kháng của motor nên điện áp chân S gần bằng điện áp nguồn là 12V. Do yêu cầu của MOSFET, để kích dẫn MOSFET thì điện áp kích chân G phải lớn hơn chân S ít nhất 3V, nghĩa là ít nhất 15V trong khi chúng ta dùng vi điều khiển để kích MOSFET, rất khó tạo ra điện áp 15V. Như thế MOSFET kênh N không phù hợp để làm các khóa phía trên trong mạch cầu H (ít nhất là theo cách giải thích trên). MOSFET loại P thường được dùng trong trường hợp này. Tuy nhiên, một nhược điểm của MOSFET kênh P là điện trở dẫn DS của nó lớn hơn MOSFET loại N. Vì thế, dù được thiết kế tốt, MOSFET kênh P trong các mạch cầu H dùng 2 loại MOSFET thường bị nóng và dễ hỏng hơn MOSFET loại N, công suất mạch cũng bị giảm phần nào. Hình 13 thể hiện một mạch cầu H dùng 2 loại MOSFET tương đồng.

Hình 13. Mạch cầu H dùng MOSFET.

Tôi dùng 2 MOSFET kênh N IRF540 và 2 kênh P IRF9540 của hãng International Rectifier làm các khóa cho mạch cầu H. Các MOSFET loại này chịu dòng khá cao (có thể đến 30A, danh nghĩa) và điện áp cao nhưng có nhược điểm là điện trở dẫn tương đối lớn (bạn tìm đọc datasheet của chúng để biết thêm). Phần kích cho các MOSFET kênh N bên dưới thì không quá khó, chỉ cần dùng vi điều khiển kích trực tiếp vào các đường L2 hay R2. Riêng các khóa trên (IRF9540, kênh P) tôi phải dùng thêm BJT 2N3904 để làm mạch kích. Khi chưa kích BJT 2N3904, chân G của MOSFET được nối lên VS bằng điện trở 1K, điện áp chân G vì thế gần bằng VS cũng là điện áp chân S của IRF9540 nên MOSFET này không dẫn. Khi kích các line L1 hoặc R1, các BJT 2N3904 dẫn làm điện áp chân G của IRF9540 sụt xuống gần bằng 0V (vì khóa 2N3904 đóng mạch). Khi đó, điện áp chân G nhỏ hơn nhiều so với điện áp chân S, MOSFET dẫn. Vi điều khiển có thể được dùng để kích các đường L1, L2, R1 và R2.

(nguồn: hocarv)